半導体製品をけん引する IT のメガトレンドに従って半導体を作る場合、どのような技術が主力になるでしょうか。IT のトレンドである AI と IoT、5G に関する半導体技術とは何でしょうか。ズバリ、高集積化とソフトウエアの集積になります。このため微細化の進展、3 次元 IC 化、ソフトウエアがカギとなります。連載の最後に半導体側の技術を紹介します。

AI では、ニューラルネットワークを利用する積和演算回路とメモリ、それらを制御するコントローラなどが集積されています。これらの回路は集積度が上がれば上がるほど性能向上、低消費電力化、小型化などのメリットが生きてくるため微細化プロセスを使います。5G でも大量の通信トラフィックや、データレートの高速化、ミリ波でのビームフォーミング技術などが必要となってくるため微細化プロセスへ移行します。

微細化とは言うものの、実際の配線幅や配線間隔の微細化のスピードは鈍ってきています。これまでのようにスケーリング(比例縮小側)によって約 2/3 ずつ寸法を微細化してくる技術は 20nm あたりから鈍ってきました。20nm から 19nm、18nm へと少しずつ細いという技術になってきています。世間では、インテルの 10nm プロセスと TSMC の 7nm プロセスの線幅はほぼ同じくらいと言われています。今や、半導体製造メーカーがいう 5nm ノード、3nm ノードなどという数字と実際の寸法とはかなりかけ離れています。例えば 7nm ノードでは、配線幅と間隔を足した配線ピッチは 40nm 程度です。

ではどうやって「微細化」しているのでしょうか。それは集積回路の技術基準がプロセスの最小寸法から PPA(Power, Performance, Area:性能、消費電力、面積)に変わってきたことと深く関係します。つまり、従来の比例縮小側から面積縮小側(エリアスケーリング)にシフトして面積を小さくするようになってきたのです。トランジスタは平面的なプレーナ型から 3 次元構造の FinFET に変わり、配線は 2 次元でトランジスタからトランジスタへつないでいた方法から、立体的に 3 次元構造にして経路を短縮してつなぐように変わってきたのです。そうすると配線をそれほど微細にしなくても単位面積あたりに集積できる回路を増やすことができます。

このようなプロセス上で 3 次元化することによって、単位面積当たりのトランジスタ数を増やすことができるようになりました(図 1)。メーカーによってはこれを密度スケーリング(Density scaling)と呼んだり、DTCO(Design Technology Co-Optimization)と呼んだりします。

図1 エリアスケーリングは立体構造で面積を縮小 出展 Semiconductor (YouTube チャンネル)

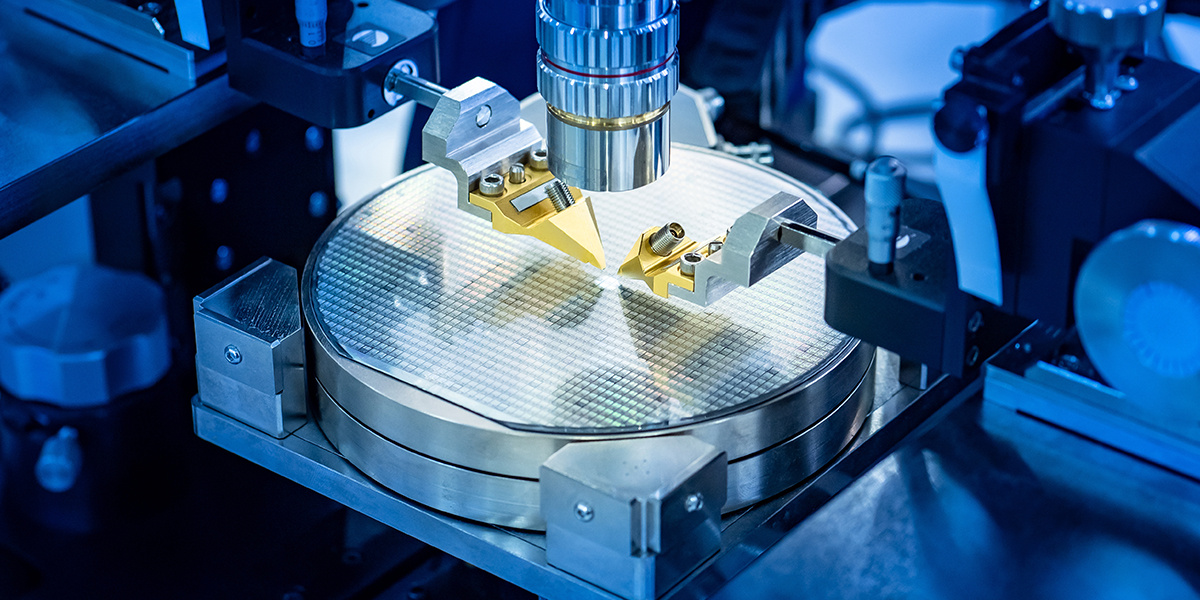

そしてもう一つの手法が 3D-IC です。これば、チップを 3 次元的に重ねていく手法です。配線部分はチップの表面から裏面側に貫通して通す TSV(Through Silicon Via)と呼ばれる技術を使います。3 次元に重ねたチップを最後にプラスチックで封止して外見上は従来の IC とは変わらないように作ります。

最近は 3D-IC だけではありません。先端パッケージと呼ばれる手法が登場しています。これは大手ファウンドリが述べているように、1 チップでの集積度よりも 10 倍も集積度を上げることのできる現実的な手法です。

さらに、チップレット(chiplet)と呼ばれる IC 上の一部の回路ブロックをチップとして切り出したものが登場してきました。これは従来なら一つのチップ上に多数の回路ブロックを集積し、それらを配線でつないでいますが、重要な回路ブロックだけをチップレットとして切り出し、ほかのチップと重ねて 3D-IC とする方がチップ全体の面積が小さくなります。

このような先端パッケージは従来ならコストがかさむため商用化は難しいと見られていました。しかし、先に述べた DTCO の手法では、IC 上の様々な回路ライブラリを一つのプロセスノードで 3 次元構造になるように作り直していました。次のプロセスノードになると再び、それに合うように作り直さなければなりません。従来の比例縮小側なら単純に寸法を約 2/3 になるように微細化するだけでしたが、DTCO では 3 次元構造に合うように作り直す必要があります。これではウェーハコストは上がるばかりです。つまり微細なプロセスノードに移行するにつれ、ファウンドリのウェーハ価格は上がっていきます(図 2)。この上昇傾向を外挿すると、2nm プロセスノードになると 7nm ノードの 5 倍ほどのウェーハ価格になります。このような高価なファウンドリウェーハをユーザーは受け入れてくれるでしょうか?

図 2 ウェーハ価格は微細化と共に上昇

それを考えると、先端パッケージの方がむしろ安く作製できるようになります。現実に AMD は低コストの点で先端パッケージを採用し始めています。

IC の集積度が高くなると、専用のハードワイヤードの回路ではなく CPU を搭載しソフトウエアで機能を差別化する方向に変わってきました。いわゆる SoC(System on chip)は CPU だけでなく、GPU や DSP 等様々な専用プロセッサを集積した回路です。これらのプロセッサにはソフトウエアをメモリに集積しておき、そのソフトウエアを変えるだけで SoC の機能を変えることができます。

もう一つ、機能をハードウエアとして変えられるデバイスもあります。これが FPGA(Field Programmable Gate Array)と呼ばれるICです。

つまりソフトウエアで機能を変えられる CPU などのプロセッサと、ハードウエアで機能を変えられる FPGA があればどのような新機能も実現できます。このためソフトウエアやアルゴリズムなどで独自性を SoC に織り込み、差別化した製品を作ることができます。今後は、様々なプロセッサを集積したヘテロプロセッサや FPGA 回路を集積した SoC がハイエンド製品として普及してくることでしょう。

著者:津田 建二

国際技術ジャーナリスト、セミコンポータル編集長

現在、英文・和文のフリー国際技術ジャーナリストとして活躍。長年、半導体・エレクトロニクス産業を取材。ブログやメディアを通じて半導体産業にさまざまな提案をしている。海外の技術ジャーナリストとも幅広いネットワークを持つ。