連載企画「半導体産業の現状と未来」の第 3 回目です。

半導体・エレクトロニクス産業を長年に渡り取材してきた、国際技術ジャーナリストの津田建二氏が、半導体業界の歴史や半導体技術、さらに未来を語ります。

第 3 回:半導体は水平分業の歴史:垂直統合から水平分業へ

半導体産業は水平分業でやってきました。古くは結晶産業、製造装置産業、そして設計ツール産業、ファブレス半導体、ファウンドリ、OSAT などさまざまな形で分業してきました。半導体メーカーは、設計と製造を共に手掛ける IDM(垂直統合メーカー)、ファブレス、ファウンドリ、OSAT に分かれています。しかもメモリやアナログは IDM ですが、ロジックやプロセッサはファブレスとファウンドリにまとまっています。今後は何が出てくるのでしょうか。

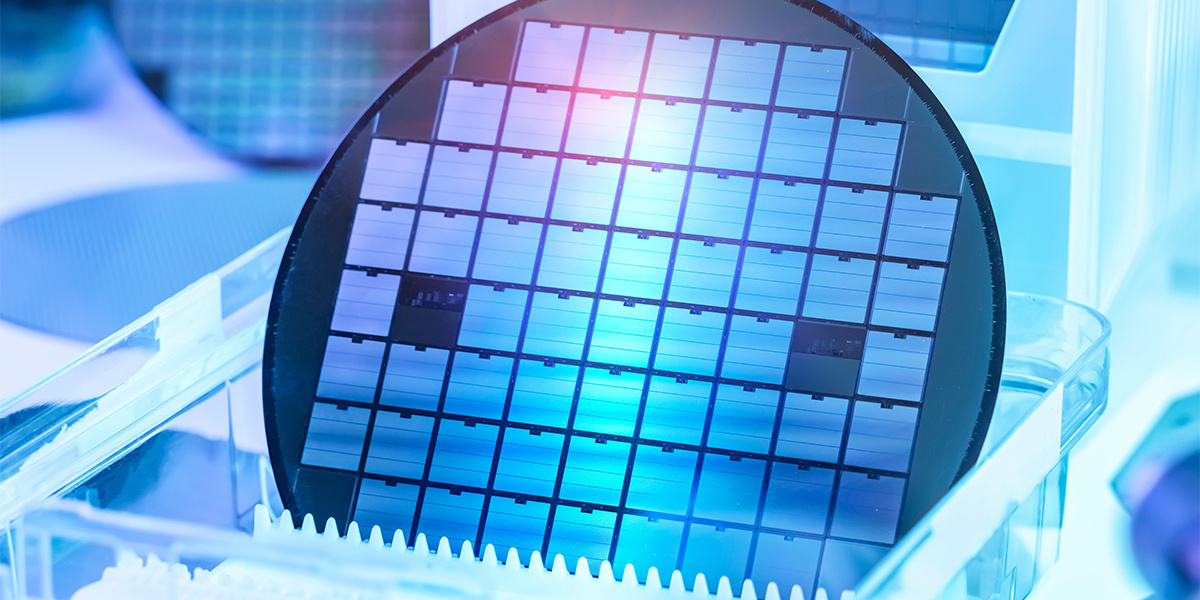

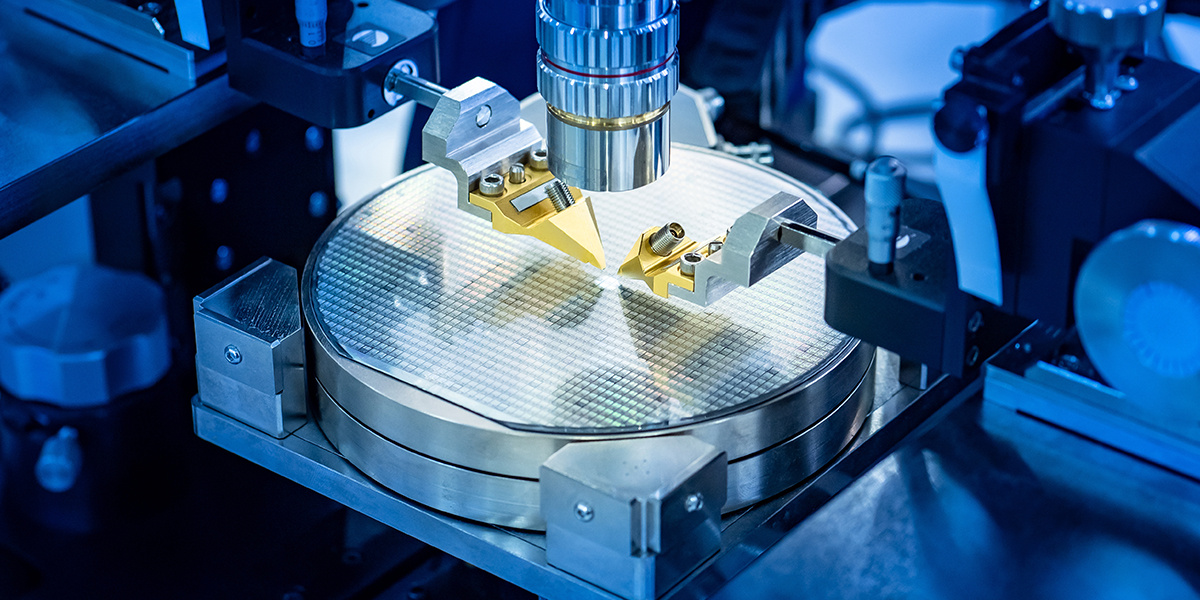

半導体産業が生まれた時は、半導体結晶作りから始まり、それを拡散やアニールなどの熱処理するための炉心菅や簡単なテスターなども手作りでした。しかし、シリコンの結晶技術が確立し、リソグラフィ技術によるパターン形成技術などが確立するにつれ、半導体製造装置を作るメーカーが登場してきました。半導体メーカーが製造装置などを作るのではなく、専門の製造装置メーカーや計測器メーカー、フォトマスクメーカーなどが設立され、産業として形成されるようになりました(図1)。

図1. 半導体産業は分業の歴史(出典:筆者作成)

また、当初のディスクリートトランジスタから集積化へ進み回路が次第に複雑になってくると、回路部門とプロセス部門が半導体メーカー内に形成されました。小規模な IC やアナログ IC だとマスク設計は回路エンジニアが作図して、それをマスクメーカーに渡すようになりました。デジタル化が進むと共に回路が複雑になると設計に時間がかかり人手からコンピュータによる自動化へと移りました。ここに EDA ベンダーが生まれました。

半導体メーカーとしても工場を建てるほどの資金はないが設計だけならできるというファブレス半導体企業が米国西海岸で続々と誕生しました。ASIC と呼ばれる専用 IC や FPGA というロジック回路をプログラムして独自回路を作れる IC を作るメーカーがファブレスとなりました。工場で生産する数量を考えなくてもよいのです。一方で、半導体工場を持たない企業は男のすることではない、と述べ、ファブレスの台頭を苦々しく思っていた経営者が米国にいましたが、ファブレスの流れは止められませんでした。

市場調査会社の IC Insights の調べでは(図2)、全半導体メーカーの売上額に占めるファブレス半導体メーカーの売上額の比率は毎年上がってきて、2021 年には全半導体産業の売上額の 34.8% を占めるようになりました。今でも増え続けています。

図2. ファブレス半導体の勢いは止まらない(出典:IC Insights)

それを補うための製造プロセス専門のファウンドリメーカーも生まれてきました。台湾の英雄と言われるモーリス・チャン氏が TSMC を始めました。それに続けとばかりに台湾では UMC もファウンドリを始め、AMD 社もファブレスの AMD とファウンドリの Global Foundries に分かれていきました。さらにイスラエルからも Tower Semiconductor、ドイツでは X-Fab、中国でも SMIC などが登場しました。このようにして、ファブレスとファウンドリが半導体産業を形成するようになりました。

設計が人手から自動化に移ると、設計ツールを提供する企業が生まれてきました。日本では半導体メーカー内で作ってきた CAD 開発部門が自社ツールから、設計ツールベンダーに替えるようになりました。自社内でバージョンアップや改善作業を続けるよりも外部調達の方が便利で速いからです。

そしてファブレス企業にとっては、設計手法の教科書も登場しました。カリフォルニア工科大学のカーバー・ミード教授とゼロックス社エンジニアのリン・コンウェイ氏が書いた「Introduction to VLSI Systems」という本です。設計者のバイブル的な存在になりました。

半導体産業をよく見ますと、回路が複雑な大規模のデジタル IC はファブレス、設計が比較的単純なメモリや、規模の小さなアナログ回路、ディスクリートは IDM(設計も製造も手掛ける垂直統合メーカー)が担っています。唯一の例外だったインテルも最近はファウンドリ事業を始めており、半導体産業の分業化はますます進んでいます。

更なる分業は続く

最近では技術が進むにつれ、更なる分業も進んでいます。ファブレスと言っても設計仕様を記述し RTL(Register Transfer Level)までは出力しますが、ここまでしか手掛けない企業もいます。その後のネットリストや論理合成、さらにレイアウトや配線設計、そしてマスク出力までを行うデザインハウスも出てきています。マスク出力まで設計しないとファウンドリは、製造プロセスに進めないからです。

また論理設計の最初の段階での RTL 出力は、プログラミング作業であるため、バグなどの心配を取り除くための検証作業も伴います。この検証作業用のツールも販売されている上に、検証作業だけを請け負う企業も出てきています。

ファウンドリで製造した後に、半導体製品とするために後工程でチップをパッケージングします。チップ上の狭くて細い配線パッド(数 10µm 幅)を外部へ取り出せる大きさ(数ミリ幅)に変換し、かつチップを外部の湿気から守るためのモールド樹脂でのパッケージに封止します。この後工程を専門とする請負メーカーは OSAT (オーサット:Outsourced Semiconductor Assembly and Test)と呼ばれます。パッケージに封止してからテストを行い、良品・不良品を自動機で選別します。

ところが最近は、チップや IP(SoC 内の一部の回路)などのチップレットをいろいろ組み合わせて基板に載せ、配線して集積回路を作るという作業が出てきました(図3)。ファウンドリと OSAT の間に来る作業になります。この作業は OSAT とファウンドリの両者が手掛けており、今の所、第三者(Third party)が分業するという体制にはなっていません。しかし、将来はチップレットをパッケージに実装するという第三者が出てくる可能性はあります。

図3. チップやチップレットを実装して1パッケージに封止する 2.5D/3D-IC(出典:UCIe)

チップレットや IP を回路基板上で配置し、そのピンの配置や寸法などを標準化してどのようなチップでもつなげるようにしようという標準化団体 UCIe が出来ています。そうすると、このパッケージングを専門に手掛ける企業が登場しやすくなります。ただ、唯一の心配は、この団体に日本企業が 1 社も参加していないことです。

著者:津田 建二

国際技術ジャーナリスト、セミコンポータル編集長

現在、英文・和文のフリー国際技術ジャーナリストとして活躍。長年、半導体・エレクトロニクス産業を取材。ブログやメディアを通じて半導体産業にさまざまな提案をしている。海外の技術ジャーナリストとも幅広いネットワークを持つ。