# MT7931AN Datasheet 802.11a/b/g/n/ac/ax Wi-Fi 1T1R + Bluetooth 5.0 + ARM® Cortex®-M33

Version: 1.1

Release date: 2022-11-25

Use of this document and any information contained therein is subject to the terms and conditions set forth in <a href="Exhibit 1">Exhibit 1</a>. This document is subject to change without notice.

# **Document Revision History**

| Revision | Date       | Author   | Description                                                                                                                                                                                                         |

|----------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | 2020-08-14 | MediaTek | Initial draft                                                                                                                                                                                                       |

| 0.2      | 2020-08-23 | MediaTek | <ol> <li>Update RF WF block diagram (remove AUX port)</li> <li>Update block diagram</li> <li>Remove SPI Slave part</li> <li>Add pin list, function description, pin multiplexing and package information</li> </ol> |

| 0.9      | 2021-03-17 | MediaTek | <ol> <li>Add section 2.1 PMU</li> <li>Add section 2.3 peripherals</li> <li>Add section 2.4 audio system</li> <li>Add chapter 4 electrical characteristics</li> </ol>                                                |

| 0.92     | 2021-07-15 | MediaTek | 1. Revised version                                                                                                                                                                                                  |

| 0.93     | 2021-08-05 | MediaTek | 1. Revised 3.2.2 BLE TX Max. Power                                                                                                                                                                                  |

| 0.94     | 2021-11-14 | MediaTek | Update the PinMux table, RF performance, LP data,     power-on sequence and top marking                                                                                                                             |

| 0.95     | 2022-02-15 | MediaTek | <ol> <li>Add thermal characteristics</li> <li>Update 2.1.3 power performance data</li> </ol>                                                                                                                        |

| 0.96     | 2022-04-30 | MediaTek | 1. Update 3.2.3 and 3.2.5 BLE TX power                                                                                                                                                                              |

| 0.97     | 2022-05-26 | MediaTek | <ol> <li>Update ESD (HBM) value</li> <li>Update Table 2-1</li> </ol>                                                                                                                                                |

| 1.0      | 2022-11-07 | MediaTek | <ol> <li>Add legacy sleep mode in Table2-1</li> <li>Update WiFi feature</li> <li>Update PinMux I2C pin direction and description</li> <li>Remove GPIO_R_8/GPIO_R_10</li> </ol>                                      |

| 1.1      | 2022-11-25 | MediaTek | All content is same as v1.0, only update MediaTek     document secure label                                                                                                                                         |

# **Table of Contents**

| Docu  | ment    | Revisior | History       |                            | 2  |

|-------|---------|----------|---------------|----------------------------|----|

| Table | e of Co | ntents   |               |                            | 3  |

| 0     | Feat    | ures     |               |                            | 8  |

| 1     | Syste   | em Over  | view          |                            | 9  |

|       | 1.1     | Gener    | al Descript   | ion                        | 9  |

|       | 1.2     | Featu    | es            |                            | 9  |

|       |         | 1.2.1    | Technolo      | gy and Package             | 9  |

|       |         | 1.2.2    | Power M       | anagement and Clock Source | 9  |

|       |         | 1.2.3    | Platform      |                            | 9  |

|       |         | 1.2.4    | Wi-Fi         |                            | 10 |

|       |         | 1.2.5    | Bluetoot      | h                          | 10 |

|       |         | 1.2.6    | Miscellar     | neous                      | 10 |

|       | 1.3     | Block    | Diagram       |                            | 11 |

| 2     | Func    | tional D | escription    |                            | 12 |

|       | 2.1     | Power    | · Managem     | nent Unit                  | 12 |

|       |         | 2.1.1    | Introduct     | tion                       | 12 |

|       |         | 2.1.2    | Chip Pow      | ver Plan                   | 12 |

|       |         | 2.1.3    | Power Pe      | erformance                 | 15 |

|       |         | 2.1.4    | Power St      | ate                        | 16 |

|       | 2.2     | Syster   | n Initializat | ion                        | 16 |

|       |         | 2.2.1    | Chip Pow      | ver-On                     | 16 |

|       |         | 2.2.2    | Bootstra      | p Function                 | 17 |

|       |         | 2.2.3    | System B      | oot Sequence               | 18 |

|       | 2.3     | Applic   | ation Proc    | essor Subsystem Cortex-M33 | 18 |

|       |         | 2.3.1    | CPU           |                            | 18 |

|       |         | 2.3.2    | Cache an      | d Tightly Coupled Memory   | 18 |

|       | 2.4     | Periph   | erals         |                            | 19 |

|       |         | 2.4.1    | Serial NO     | R Flash Controller         | 19 |

|       |         |          | 2.4.1.1       | Introduction               | 19 |

|       |         |          | 2.4.1.2       | Features                   | 19 |

|       |         |          | 2.4.1.3       | Block Diagram              | 20 |

|       |         |          | 2.4.1.4       | Read Flash                 | 22 |

|       |         | 2.4.2    | Auxiliary     | ADC Function               | 22 |

|       |         |          | 2.4.2.1       | Functional description     | 22 |

|       |         |          | 2.4.2.2       | Features and IO            | 23 |

|       |         | 2.4.3    | SPI Maste     | er Controller              | 24 |

|       |         |          | 2.4.3.1       | Functional Description     | 24 |

|       |         |          | 2.4.3.2       | Pin Description            | 24 |

|       |         |          | 2.4.3.3       | Transmission Formats       | 24 |

|     |         | 2.4.3.4   | Features     |                                     | 25 |

|-----|---------|-----------|--------------|-------------------------------------|----|

|     | 2.4.4   | SDIO Slav | /e           |                                     | 27 |

|     |         | 2.4.4.1   | Functional   | Description                         | 27 |

|     |         | 2.4.4.2   | Features     |                                     | 27 |

|     |         | 2.4.4.3   | Block Diag   | ram                                 | 28 |

|     |         | 2.4.4.4   | Functions    | Description                         | 28 |

|     |         | 2.4.4.5   | Pin descrip  | otion                               | 29 |

|     |         | 2.4.4.6   | SDIO Timir   | ng Waveform (3.3V)                  | 30 |

|     | 2.4.5   | I2C       |              |                                     | 32 |

|     |         | 2.4.5.1   | Introduction | on                                  | 32 |

|     |         | 2.4.5.2   | Features     |                                     | 32 |

|     |         | 2.4.5.3   | Block Diag   | ram                                 | 33 |

|     | 2.4.6   | UART      |              |                                     | 34 |

|     |         | 2.4.6.1   | Introduction | on                                  | 34 |

|     |         | 2.4.6.2   | Features     |                                     | 34 |

|     | 2.4.7   | PWM       |              |                                     | 35 |

|     |         | 2.4.7.1   | Functions    | Description                         | 35 |

|     | 2.4.8   | DMA       |              |                                     | 36 |

|     |         | 2.4.8.1   | Command      | Queue (CQ) DMA                      | 36 |

|     |         | 2.4.8.2   | Application  | n Processor (AP) DMA                | 36 |

|     |         |           | 2.4.8.2.1    | Peripheral DMA                      | 37 |

|     |         |           | 2.4.8.2.2    | Virtual FIFO                        | 37 |

|     |         |           | 2.4.8.2.3    | APDMA Channels and Priority Control | 38 |

|     | 2.4.9   | GPT       |              |                                     | 39 |

|     |         | 2.4.9.1   | Introduction | on                                  | 39 |

|     |         | 2.4.9.2   | Features     |                                     | 39 |

|     |         | 2.4.9.3   | Block Diag   | ram                                 | 40 |

|     |         | 2.4.9.4   | Theory of    | Operations                          | 40 |

|     | 2.4.10  | WDT       |              |                                     | 41 |

|     |         | 2.4.10.1  | Introduction | on                                  | 41 |

|     |         |           |              | Description                         |    |

|     |         |           |              | fication for CM33                   |    |

|     | 2.4.11  |           |              |                                     |    |

|     |         |           |              |                                     |    |

|     |         |           | -            | or Down Control Truth Table         |    |

| 2.5 | Interru | pt        |              |                                     | 44 |

|     | 2.5.1   |           |              |                                     |    |

|     | 2.5.2   |           |              |                                     |    |

|     | 2.5.3   | •         |              |                                     |    |

|     |         |           |              |                                     |    |

| 3.1 |         |           |              |                                     |    |

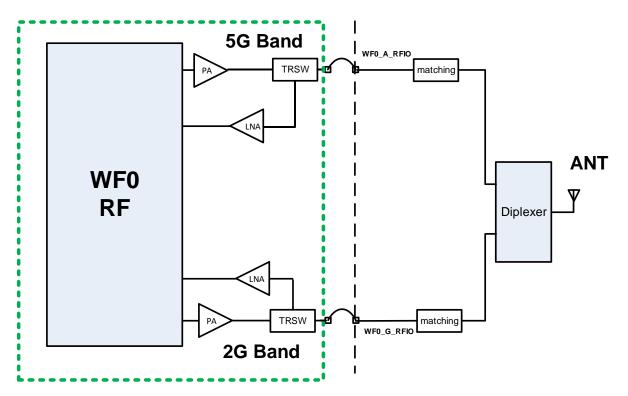

|     | 3.1.1   | Wi-Fi RF  | Block Diagra | m                                   | 51 |

3

part, is strictly prohibited

|       |         | 3.1.2     | Wi-Fi RF 2.4G Band Receiver Specifications           | 51 |

|-------|---------|-----------|------------------------------------------------------|----|

|       |         | 3.1.3     | Wi-Fi RF 2.4G Band Transmitter Specifications        | 53 |

|       |         | 3.1.4     | Wi-Fi RF 5G Band Receiver Specifications             | 53 |

|       |         | 3.1.5     | Wi-Fi RF 5G Band Transmitter Specifications          | 55 |

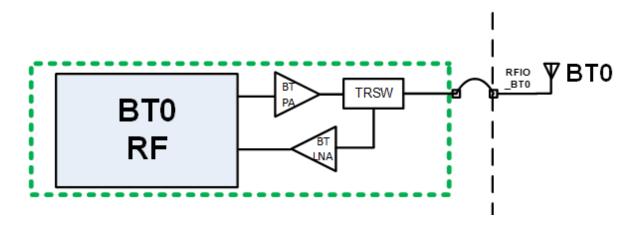

|       | 3.2     | Blueto    | ooth Radio Characteristics                           | 55 |

|       |         | 3.2.1     | Bluetooth RF Block Diagram                           | 55 |

|       |         | 3.2.2     | Bluetooth LE un-coded PHY Receiver Specifications    | 56 |

|       |         | 3.2.3     | Bluetooth LE Un-Coded PHY Transmitter Specifications | 57 |

|       |         | 3.2.4     | Bluetooth LE Coded PHY Receiver Specifications       | 58 |

|       |         | 3.2.5     | Bluetooth LE Coded PHY Transmitter Specifications    | 58 |

| 4     | Electi  | rical Cha | aracteristics                                        | 60 |

|       | 4.1     | Absolu    | ute Maximum Rating                                   | 60 |

|       | 4.2     | Recon     | nmended Operating Range                              | 60 |

|       | 4.3     | DC Ch     | aracteristics                                        | 60 |

|       | 4.4     | XTAL (    | Oscillator                                           | 61 |

|       | 4.5     | PMU (     | Characteristics                                      | 61 |

|       | 4.6     | Auxilia   | ary ADC Characteristics                              | 62 |

|       | 4.7     | Therm     | nal Characteristics                                  | 63 |

| 5     | Packa   | age Spe   | cification                                           | 65 |

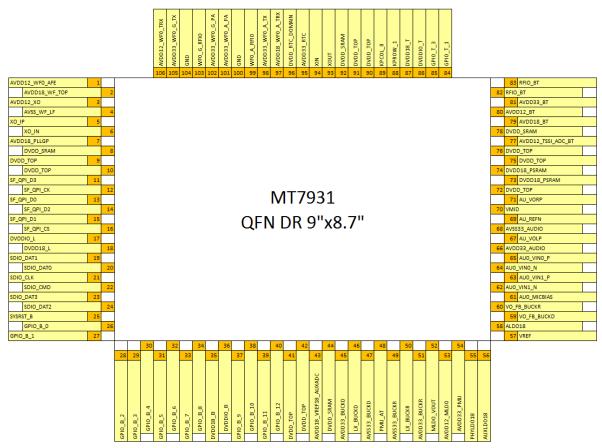

|       | 5.1     | Pin La    | yout                                                 | 65 |

|       | 5.2     | Pin De    | escription                                           | 66 |

|       | 5.3     | PinMu     | JX                                                   | 69 |

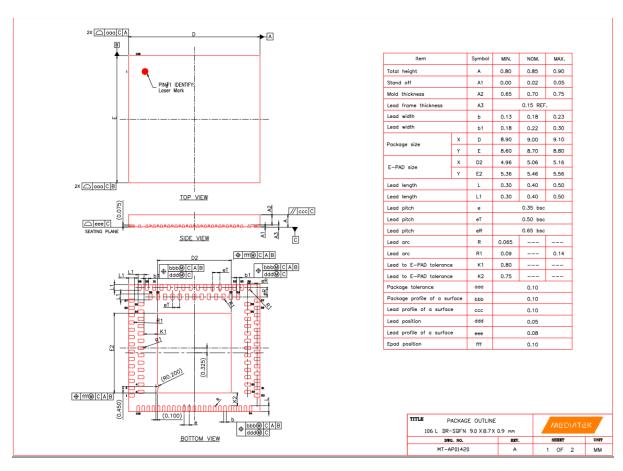

|       | 5.4     | Packa     | ge Information                                       | 75 |

|       | 5.5     | Order     | Information                                          | 76 |

|       | 5.6     | Top M     | 1arking                                              | 76 |

| Exhib | it 1 Te | rms and   | d Conditions                                         | 77 |

# **Lists of Figures and Tables**

| Figure 1-1 MT7931AN System-On-Chip block diagram           | 11 |

|------------------------------------------------------------|----|

| Figure 2-1 Power grid                                      | 13 |

| Figure 2-2 PMU power on sequence                           |    |

| Figure 2-4 Power-On sequence                               | 17 |

| Figure 2-5. Serial NOR flash controller block diagram      | 21 |

| Figure 2-6. Read operation sequence                        | 22 |

| Figure 2-7 Auxiliary ADC block diagram                     |    |

| Figure 2-8 Auxiliary ADC analog IP block diagram           | 23 |

| Figure 2-9 Pin connection between SPI master and SPI slave | 24 |

| Figure 2-10 SPI transmission formats                       | 24 |

| Figure 2-11 Operation flow with or without PAUSE mode      | 25 |

| Figure 2-12 CS_N deassert mode                             | 26 |

| Figure 2-13 SDIO controller block diagram                  | 28 |

| Figure 2-14 Signal connections to 4-bit SDIO cards         | 29 |

| Figure 2-15 Bus signal levels                              | 30 |

| Figure 2-16 Bus timing diagram (default)                   | 30 |

| Figure 2-17 High-speed timing diagram                      | 31 |

| Figure 2-18 Block diagram of I2C                           | 33 |

| Figure 2-19 PWM patterns                                   | 35 |

| Figure 2-20 APDMA Block Diagram                            | 37 |

| Figure 2-21 Virtual FIFO Concept                           | 38 |

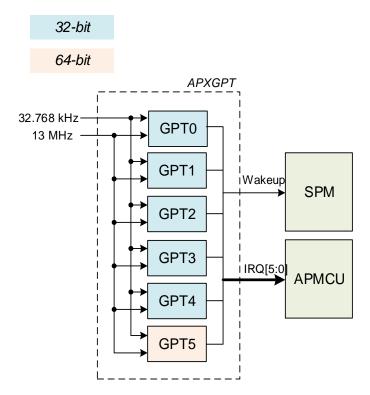

| Figure 2-22 Block Diagram of APXGPT                        | 40 |

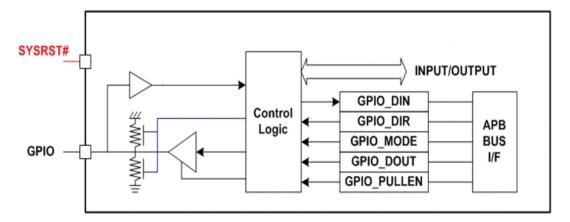

| Figure 2-23 MT7931AN GPIO Controller                       | 42 |

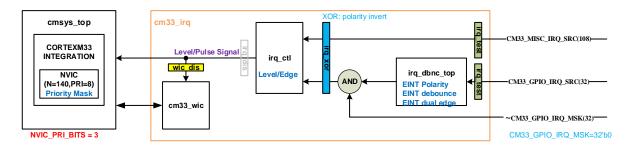

| Figure 2-24 CM33_IRQ Block Diagram                         | 44 |

| Figure 3-1 Wi-Fi RF block diagram                          | 51 |

| Figure 3-2 Bluetooth RF block diagram                      | 55 |

| Figure 5-1 Package ball-out                                | 65 |

| Figure 5-2. Package outline drawing                        | 75 |

| Figure 5-3 Top marking                                     | 76 |

| Table 2-1 MT7931AN platform power modes                    | 16 |

| Table 2-2 MT7931AN strapping pins and modes                | 17 |

| Table 2-3 SPI controller interface                         | 24 |

| Table 2-4 SDIO pin definitions                             | 29 |

| Table 2-5 Bus signal voltage                               | 30 |

| Table 2-6 Bus timing parameter values (default)            | 31 |

| Table 2-7 High-speed timing parameter values               | 32 |

| Table 2-8 DMA type for hardware IP                         | 38 |

| Table 2-9 Operation Mode of GPT                            | 39 |

| Table 2-10 PU/PD resistance Spec                           | 43 |

| Table 2-11 CM33 interrupt                                  | 45 |

| Table 4-1 Absolute maximum rating                          | 60 |

| Table 4-2 Recommended operating range                      | 60 |

| Table 4-3 DC characteristics                               | 60 |

# **UNCLASSIFIED**

| Table 4-4 XTAL oscillator requirement                                                    | 61 |

|------------------------------------------------------------------------------------------|----|

| Table 4-5 PMU electrical characteristics                                                 | 61 |

| Table 4-6 ADC specification                                                              | 62 |

| Table 4-7-1 Thermal characteristics                                                      | 64 |

| Table 4-7-2 Thermal characteristics                                                      | 64 |

| Table 5-1. Pin descriptions                                                              | 66 |

| Table 5-2 Digital IO pin configuration in each pad and the corresponding pin description | 69 |

| Table 5-3 Order information                                                              | 76 |

# 0 Features

#### Wi-Fi

- IEEE 802.11 1T1R a/b/g/n/ac/ax 5 GHz and 2.4 GHz bands

- Supports 1x1 20 MHz bandwidth, MCS0~8(256-QAM) in 2.4/5 GHz band

- Support MU-MIMO RX

- Support uplink MU-OFDMA TX and downlink MU-OFDMA RX

- Support Tx LDPC(Low-density parity check)

- Support Rx Beamformee

- Support RX STBC

- Wi-Fi security WFA WPA/WPA2/WPA3 personal

- QoS support of WFA WMM

- Integrated balun, PA, LNA, and T/R switch

- Support CSI (Channel Signal Information)

- Supports antenna diversity

- Optional external LNA and PA support

#### **Bluetooth**

- BT5.0 2M\_PHY / Long Range / Advertising

Extension / SAM / CS#2 / High Duty Cycle Non-Connectable ADV

- BT4.2 Link Layer Privacy / LE Secure

Connection / LE Data Packet Length Extension

/ Link Layer Extended Scanner Filter Policies

- BT4.1 Link Layer Topology / Secure Connection

- BT4.0 BLE only mode

- Integrated balun and PA

- Up to 8 BLE links

- Packet loss concealment

- Channel quality driven data rate adaptation

- Channel assessment and WB RSSI for AFH

# Microcontroller Subsystem

- ARM® Cortex®-M33 with floating point unit (FPU) with 300MHz clock rate

- Supports 12 DMA channels

- Embedded 4MB pSRAM for applications

- Supports external serial flash with Quad

Peripheral Interface (QPI) mode

- Supports eXecute In Place (XIP) on flash

- Supports interfaces: SDIO, SPI master, I2C, I2S, IR input, UART, AUXADC, PWM, and GPIOs

#### Secure Boot and Crypto Engine

- Secure boot from serial flash

- Hardware crypto engines including AES, DES/3DES, and SHA

#### **Clock Source**

- 26-MHz crystal oscillator

- 32-kHz external or internal crystal oscillator

#### Miscellaneous

Advanced TDD Wi-Fi/Bluetooth coexistence scheme

# 1 System Overview

# 1.1 General Description

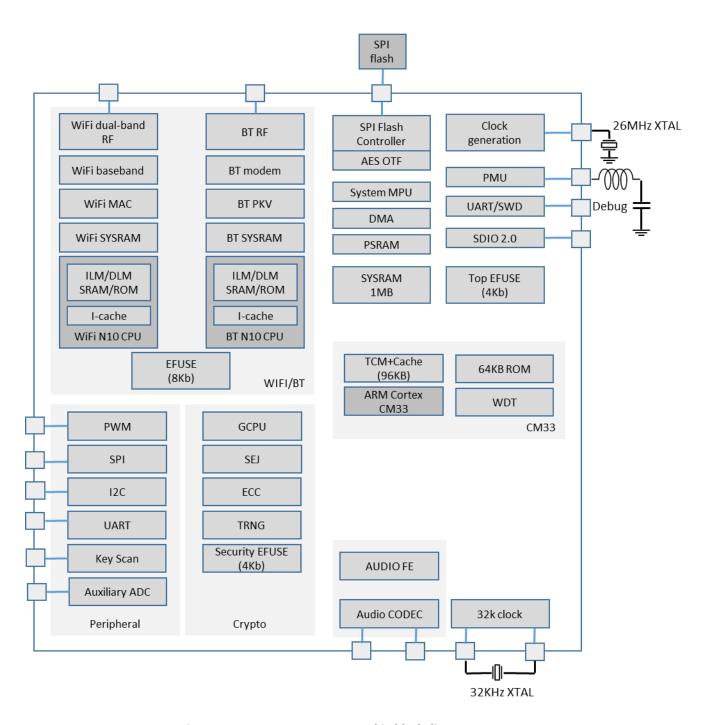

The MT7931AN is a highly integrated single chip that features an ARM® Cortex-M33 application processor, a low power 1x1 802.11a/b/g/n/ac/ax dual-band Wi-Fi subsystem, a Bluetooth v5.0 subsystem and a Power Management Unit (PMU). The Wi-Fi subsystem and a Bluetooth v5.0 subsystem offer feature-rich wireless connectivity at high standards, and deliver reliable, cost-effective throughput from an extended distance. Optimized RF architecture and baseband algorithms provide superb performance and low power consumption. The MT7931AN is designed to support standard based features in the areas of security, quality of service and international regulations, giving end users the greatest performance any time and in any circumstance. The MT7931AN is based on ARM® Cortex-M33 with floating point microcontroller (MCU) including SRAM/ROM memory. The chip also supports rich peripheral interfaces, including SDIO, SPI master, I2C, I2S, IR input, UART, AUXADC, PWM, and GPIOs.

## 1.2 Features

# 1.2.1 Technology and Package

9mm x 8.7mm DRQFN package

## 1.2.2 Power Management and Clock Source

- Integrates high efficiency power management unit with single 3.3V power supply input

- Supports a 26-MHz crystal clock with low power operation in idle mode

- Supports an external 32-kHz crystal oscillator or internal 32-kHz for low power sleep mode

#### 1.2.3 Platform

- ARM® Cortex-M33 MCU with FPU with up to 300MHz clock speed

- Supports up to 96KB for TCM and Cache memory

- Embedded 1MB SRAM

- Embedded 4MB pSRAM for applications

- Supports external serial flash with eXecute In Place (XIP) and on-the-fly AES

- Supports hardware crypto engines including AES, DES/3DES, SHA, ECC, TRNG for network security

- Supports up to 23 general purpose IOs, which are multiplexed with SPIm, UART, I2C, I2S, AUXADC, PWM and GPIO interfaces

- Supports 12 DMA channels

#### 1.2.4 Wi-Fi

- IEEE 802.11 1T1R a/b/g/n/ac/ax 5 GHz and 2.4 GHz bands

- Supports 1x1 20MHz bandwidth, MCS0~8(256-QAM) in 2.4/5 GHz band

- Support MU-MIMO RX

- Support uplink MU-OFDMA TX and downlink MU-OFDMA RX

- Support Tx LDPC(Low-density parity check)

- Support Rx Beamformee

- Support RX STBC

- Wi-Fi security WFA WPA/WPA2/WPA3 personal

- QoS support of WFA WMM

- Integrated balun, PA, LNA, and T/R switch

- Support CSI (Channel Signal Information)

- Supports antenna diversity

- Optional external LNA and PA support

#### 1.2.5 Bluetooth

- BT5.0 2M\_PHY / Long Range / Advertising Extension / SAM / CS#2 / High Duty Cycle Non-Connectable ADV

- BT4.2 Link Layer Privacy / LE Secure Connection / LE Data Packet Length Extension / Link Layer Extended

Scanner Filter Policies

- BT4.1 Link Layer Topology / Secure Connection

- BT4.0 BLE only mode

- Integrated balun and PA

- Up to 8 BLE links

- Packet loss concealment

- Channel quality driven data rate adaptation

- Channel assessment and WB RSSI for AFH

- Supports Bluetooth/Wi-Fi coexistence

## 1.2.6 Miscellaneous

- Embedded eFuse to store specific device information and RF calibration data

- Advanced TDD mode Wi-Fi/Bluetooth coexistence scheme

# 1.3 Block Diagram

Figure 1-1 MT7931AN System-On-Chip block diagram

# **2** Functional Description

# 2.1 Power Management Unit

# 2.1.1 Introduction

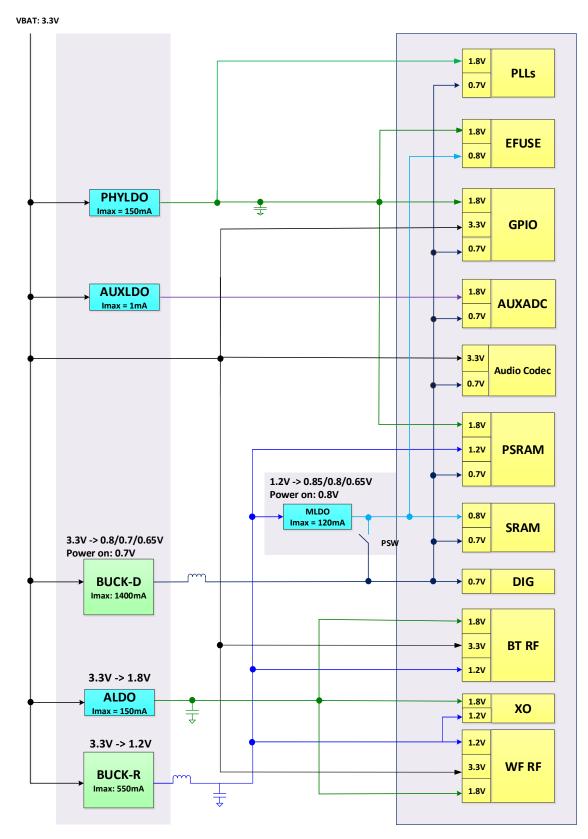

PMU contains two buck converters: BUCK-D(for digital circuit), and BUCK-R (for RF circuit) and four LDOs: PHYLDO (for PLL), AUXLDO (for AUXADC), ALDO (for XTAL) and MLDO (for on-chip memory). Please refer to Figure 2-1. Power grid for more information.

# 2.1.2 Chip Power Plan

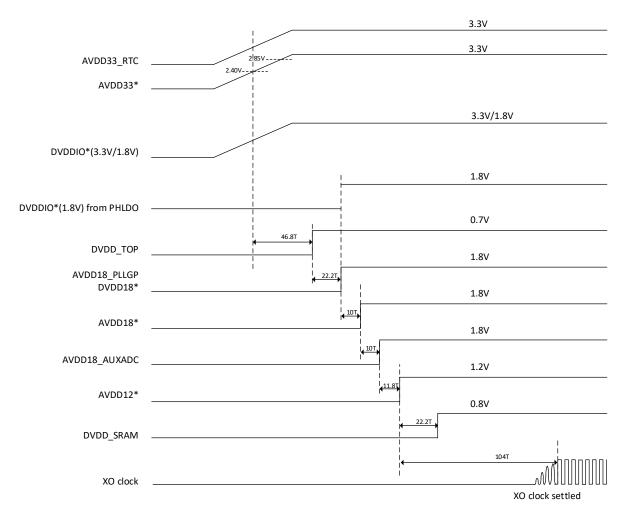

The 3.3V power source directly supplies the PMU, digital IOs (3.3V operation case), and the RF/AIP related circuitry. Figure 2-2 for PMU power on sequence.

Figure 2-1 Power grid

\*BGCLK 12.5kHz ±50% , 1T = max160us, min 53us

Figure 2-2 PMU power on sequence

# **2.1.3** Power Performance

| Operation Mode |                 | Test Conditions                                                                                                                                                                             | <b>Current Consumptions</b>                                                     | Unit |

|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|

| Power Mode     | Scenario        |                                                                                                                                                                                             | (1)                                                                             |      |

| SLEEP          | SLEEP_ext_32Khz | <ul> <li>Cortex-M33 in sleep state</li> <li>TCM 96KB SRAM is retained</li> <li>1MB SYSRAM is retained</li> <li>32-kHz XTAL</li> </ul>                                                       | 370                                                                             | μΑ   |

| ACTIVE         | Wi-Fi 2.4G TX   | <ul><li>N10 in active state</li><li>Cortex-M33 in active state</li><li>96KB TCM is active</li></ul>                                                                                         | 336@CCK 21.5 dBm<br>308@OFDM 20.5 dBm<br>222@HT20 17.5 dBm<br>202@HESU 16.5 dBm | mA   |

|                | Wi-Fi 5G TX     | <ul><li>1MB SYSRAM is active</li><li>4MB PSRAM is active</li><li>26-MHz XTAL</li></ul>                                                                                                      | 510@OFDM 21 dBm<br>372@HT20 17.5 dBm<br>354@HESU 16.5 dBm                       | mA   |

|                | Wi-Fi 2.4G RX   |                                                                                                                                                                                             | 38@HT20 MCS0<br>39@HESU20 MCS8                                                  | mA   |

|                | Wi-Fi 5G RX     |                                                                                                                                                                                             | 44@HT20 MCS0<br>47@HESU20 MCS8                                                  | mA   |

| ACTIVE & SLEEP | DTIM = 1        | <ul> <li>N10 in sleep state</li> <li>Cortex-M33 in sleep state</li> <li>96KB TCM is retained</li> <li>1MB SYSRAM is retained</li> <li>4MB PSRAM is retained</li> <li>32-kHz XTAL</li> </ul> | 2.5 (beacon = 1.6ms)                                                            | mW   |

Note: The chip variation is +/- 25%.

MediaTek Proprietary and

Confidential.

$<sup>^{(1)}</sup>$  Conditions: VBAT and VDDIO at 3.3V, temperature at 25°C, typical corner IC, XTAL at 26 MHz

#### 2.1.4 Power State

The MT7931AN platform has several power modes. You could switch the power mode depending on system use case. Please refer to Table 2-1.

| indicate a managem pendermone. |           |           |          |            |                 |            |                             |                    |                      |

|--------------------------------|-----------|-----------|----------|------------|-----------------|------------|-----------------------------|--------------------|----------------------|

| Power Modes                    | MCU clock | MCU bus   | Wi-Fi/BT | Clock      | SRAM /<br>PSRAM | Peripheral | Wake Up<br>Source           | Wake Up<br>Latency | Power<br>Consumption |

| Active                         | 300 MHz   | Active    | Off      | PLL / XTAL | Active          | On         |                             |                    | 12 mA <sup>1</sup>   |

| Idle                           | Gated     | Active    | Off      | PLL / XTAL | Active          | On         | All IRQ                     | < 1ms              | 8 mA <sup>1</sup>    |

| Legacy Sleep<br>(PSRAM On)     | Gated     | Gated     | Off      | XTAL       | Sleep<br>/ On   | On         | All IRQ                     | < 1ms              | 2.5 mA               |

| Deep Sleep                     | Power off | Power off | Off      | External   | Sleep           | Power Off  | Restricted IRO <sup>2</sup> | < 10ms             | 0.37 mA              |

Table 2-1 MT7931AN platform power modes

GPT(32K), SDIO slave, EINT, WIFI, BT, UART(CM33), RTC timer

# 2.2 System Initialization

MT7931AN system initialization is explained here in two subsections. The chip hardware power-on sequence is described in Section 2.2.1. The system boot up sequence after the secure boot master CM33 takes over the control is described in Section 2.2.3

# 2.2.1 Chip Power-On

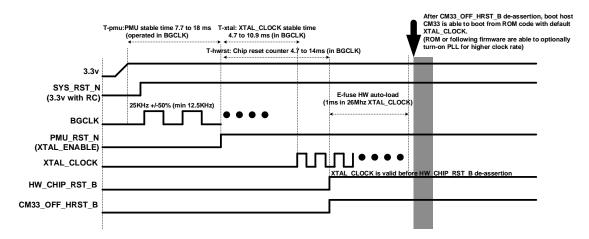

This section explains the chip power-on sequence from 3.3V power supply getting stable to the fundamental chip hardware reset de-assertion (HW\_CHIP\_RST\_B). After this fundamental chip hardware reset de-assertion, secure boot master CM33 takes over the system and boots from its ROM code.

After 3.3V power is stable, the BGCLK (band gap clock) in PMU starts to generate the 25-kHz fundamental clock, the first MT7931AN clock after power on. However, there is +/- 50% uncertainty out of this BGCLK such that this clock is only used for crystal clock control circuit. The power-on sequence is shown in the diagram below and is described in the following steps.

- Step 1: 3.3V becomes stable and PMU BGCLK starts to work for PMU initialization

- Step 2: After T-pmu (7.7 to 18ms), PMU will be valid and de-assert PMU RST N

- Step 3: After PMU\_RST\_N de-assertion, XTAL control circuit will start to work

- Step 4: After T-xtal (4.7 to 10.9ms), the crystal clock (XTAL\_CLOCK) will be valid

- Step 5: T-hwrst (4.7 to 14ms) guarantees that the XTAL\_CLOCK is valid before HW\_CHIP\_RST\_B

- Step 6: After HW\_CHIP\_RST\_B, IO setting CR will be auto-loaded from eFuse (8ms in 26 MHz)

- Step 7: Secure boot master CM33 starts to boot from its ROM

<sup>&</sup>lt;sup>1</sup> The test condition is at 25°C and 3.3V. Power consumed by connectivity is not considered.

<sup>&</sup>lt;sup>2</sup> List of modules available to signal IRQ as wake up source in deep sleep:

Note that there is a dedicated hardware input pin SYS\_RST\_N which is also able to hold the chip reset state. However, this reset will always be de-asserted before PMU\_RST\_N if the application circuit on the PCB connects this pin to some RC circuit from 3.3V power supply.

Figure 2-3 Power-On sequence

# 2.2.2 Bootstrap Function

The chip modes are sensed from the device pin during power up. After chip reset, the pull configurations are stored in a register and the settings determine the device operation mode.

| Pin name  | Pin description | Pin description | Description                                                                                         |

|-----------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------|

| GPIO_B_0  | GPIO12          | Chip Mode Sel   | 1: Normal mode: Connect 10kΩ to VCCIO_B 0: RSVD                                                     |

| GPIO_B_2  | GPIO14          | Download and    | 00: CM33 UART download mode 01: CM33 Flash normal boot mode 10: CM33 SDIO download mode             |

| GPIO_B_12 | GPIO24          | Normal boot Sel | 11: CM33 USB download mode e.g.01=GPIO_B_2 connects 10kΩ to GND, GPIO_B_12 connects 10kΩ to VCCIO_B |

| SF_QPI_CS | GPIO1           | XTAL mode Sel   | 0: XTAL buffer mode<br>1: XTAL normal mode                                                          |

Table 2-2 MT7931AN strapping pins and modes

Pins GPIO1, GPIO12, GPIO14, and GPIO24 are used for bootstrap. The system design should follow the following guidelines:

- Those pins shall not be used as input functions because the signals from other devices might affect the values sensed.

- Those pins shall not be used as an open-drain function because the pull-up resistor would affect the values

sensed.

- GPIO1 operating voltage is the same as the MT7931AN NOR flash operating voltage.

- GPIO12, GPIO14, and GPIO24 pins also act as GPIO pins; their operating voltages follow VCCIO B.

# 2.2.3 System Boot Sequence

The system boot sequence after secure boot master CM33 reset de-assertion is described as below. CM33 will boot up first from BROM, and BROM code will verify security of bootloader and execute code directly on flash by XiP. Besides the boot loader, the flash code also contains the RTOS image for CM33, and the driver and firmware necessary for Wi-Fi and Bluetooth. By executing the boot loader, CM33 will verify the security of other flash codes, then jump to RTOS entry point on flash, and fetch the corresponding driver and firmware to enable Wi-Fi and Bluetooth.

The chip initial power state is by default set to ON for Cortex-M33 platform, crypto engine, infra bus and peripherals. But the chip initial state is by default set to OFF for Wi-Fi and Bluetooth. Thus, the boot sequence will take care of the power on procedure for those subsystems before enabling them.

# 2.3 Application Processor Subsystem Cortex-M33

The MCU subsystem consists of a 32-bit MCU, the AHB/APB bus matrix, internal RAM/ROM with ROM patch function, the flash controller and the system peripherals including Direct Memory Access (DMA) engine and the General Purpose Timer (GPT).

# 2.3.1 CPU

The MT7931AN features an ARM® Cortex-M33 processor, which is the most energy efficient ARM® processor currently available. It supports the clock rates up to 200MHz when core power is 0.7V and 300MHz when core power is 0.8V. The MCU executes the Thumb-2 instruction set for optimal performance and code size, including hardware division, single cycle multiplication and bit-field manipulation. The MT7931AN includes a Memory Protection Unit (MPU) in Cortex-M33 MCU to detect unexpected memory access and provide other memory protection features. The MT7931AN also includes FPU in Cortex-M33 MCU.

## 2.3.2 Cache and Tightly Coupled Memory

The MT7931AN has a cache for Cortex-M33 to improve the efficiency of the code and data fetched from the external flash. The only cacheable memory region is the external flash. The MT7931AN also has a Tightly-Coupled-Memory (TCM), a zero-wait-state memory dedicated to Cortex-M33 and can be accessed by Cortex-M33 exclusively. It is a memory space for the critical code, including interrupt service routines that need to be executed with minimum latency. The total size of cache memory and the TCM is 96KB. We offer four software-configurable options with different cache size, TCM size and cache associativity. You can choose the best option to maximize your application's performance.

The cache system has the following features:

- Write-back (Unit: 4 words)

- Configurable 64/128/256-set, 4-way set associative (8KB/16KB/32KB)

- Each way has 64/128/256 cache lines with 8-word line size (2/4/8KB)

- 20-bit tag memory, including 19-bit high address and 1-bit valid bit

- 2-bit dirty memory. Each dirty bit records the dirtiness of half of the cache line, which is 4 words in this case.

The sizes of TCM and cache can be set to one of the following four configurations:

- 64KB TCM, 32KB cache (4-way, 256-set)

- 80KB TCM, 16KB cache (4-way, 128-set)

- 88KB TCM, 8KB cache (4-way, 64-set)

- 96KB TCM, 0KB cache (no cache)

# 2.4 Peripherals

#### 2.4.1 Serial NOR Flash Controller

# 2.4.1.1 Introduction

The MT7931AN provides one serial NOR flash controller for the convenient access to the high-speed serial NOR flash device. The controller supports single-bit SPI serial NOR flash as well as high-performance dual-bit and quad-bit SPI serial NOR flash. The speed of SPI clock could be up to 60 MHz for quad-bit SPI.

#### **2.4.1.2** Features

The serial NOR flash controller supports the following features:

- SPI bus compatible serial interface for common serial NOR flash device

- Map out 512-byte page program buffer, and support multi-page program

- Support SPI mode(single-bit) to transfer page program and 1-byte program

- Support 4-byte address mode, compatible 3-byte address mode

- Support single-bit read, dual output & dual I/O read and quad output & quad I/O read mode

- Read serial NOR flash data through direct read or PIO read mode

- Support serial NOR flash device frequency up to 60 MHz

- For direct read mode, the maximum supported capacity of serial NOR flash device is 2 Gbits. For PIO read modes, the maximum capacity is 4 Gbytes

- Support NOR flash device as follows: MX25U25635FMI, MX25U12835FMI, MX25U6432FM2I, W25Q64JW, W25Q128JW, W25Q256JW, MT25QU128

#### 2.4.1.3 Block Diagram

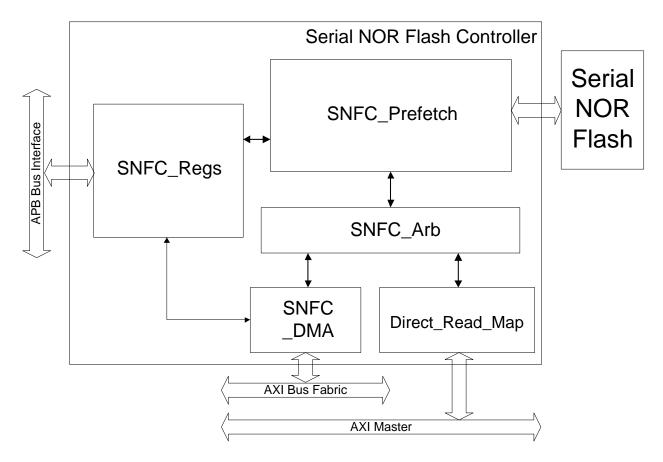

The figure below shows the block diagram of serial NOR flash controller. It contains SNFC\_Regs, SNFC\_Prefetch, SNFC\_Arb, SNFC\_DMA and Direct\_Read\_Map. The SNFC\_Regs is a register control module. The master system can access controller registers through APB interface. The SNFC\_Prefetch allocates a buffer with 128x32-bit size for read and program process. In the read process, data is first transferred to the buffer and then sent to the read master. In the program process, the whole page data should be written to the buffer and the serial NOR flash controller delivers the data to serial NOR flash device; after that the page program is triggered. The SNFC\_DMA is a HW engine to read data automatically from serial NOR flash and write data to SDRAM or SRAM through AXI bus. CPU must configure the source address, and start and end the destination address through SNFC\_Regs module before DMA (SNFC\_DMA) starts. The Direct\_Read\_Map module is used to translate the AXI master address to serial NOR flash memory address and responsible for returning data to CPU through AXI master. The SNFC\_Arb takes the arbitration's mechanism when Direct Read\_Map and SNFC\_DMA access the serial NOR flash device simultaneously.

The serial NOR flash controller handles all commands, address, data sequence and serial interface protocols. It allows users to read serial NOR flash in three ways: PIO read mode, DMA read mode and direct read mode.

- 1. For PIO read mode, CPU could program control registers (SNFC\_Regs) in a specific sequence and get the serial NOR-flash data through APB. This PIO read mode is usually used for reading data of few bytes

- 2. For DMA read mode, the SNFC\_DMA copies serial NOR flash data to SDRAM or SRAM through AXI bus

- 3. For direct read mode, the CPU could directly read serial NOR flash data through AXI bus by address offset

Figure 2-4. Serial NOR flash controller block diagram

#### 2.4.1.4 Read Flash

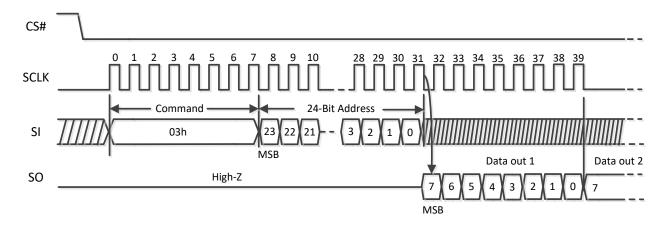

The standard SPI link format is combined with command, address and data bytes. The read operation format of single-bit SPI mode is shown in the following figure.

Figure 2-5. Read operation sequence

# 2.4.2 Auxiliary ADC Function

# 2.4.2.1 Functional description

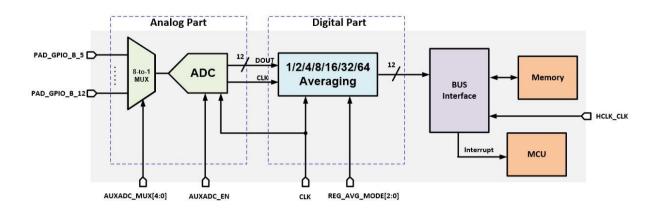

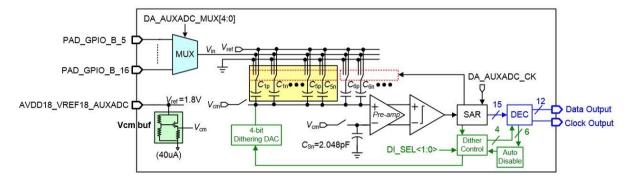

The MT7931AN features one auxiliary ADC function. The ADC function contains an 8-channel analog switch, a single-end input asynchronous 12-bit SAR (Successive Approximation Register) ADC, dithering function and a digital averaging function.

The digital averaging function can perform on-the-fly averaging function of 1/2/4/8/16/32/64 points. The ADC features the dithering function to enhance the DNL performance.

Figure 2-6 Auxiliary ADC block diagram

#### 2.4.2.2 Features and IO

The features of auxiliary ADC are listed below:

- Input channel number: 8 channels

- Sampling and output data rate: 2MS/s (default)

- DNL without dithering and averaging: <±2LSB</li>

- DNL with dithering and averaging: <±1LSB</li>

- Dithering function: 16 levels with step size of 4LSB

The IOs of auxiliary ADC can be set as either analog IO for ADC function or digital IO for GPIO function:

Analog Mode: Used for ADC application. Input voltage is 1V.

•

Figure 2-7 Auxiliary ADC analog IP block diagram

#### 2.4.3 SPI Master Controller

# 2.4.3.1 Functional Description

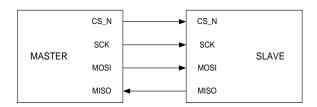

Figure 2-8 Pin connection between SPI master and SPI slave

The SPI interface is a bit-serial, four-pin transmission protocol. The above figure is an example of the connection between the SPI master and SPI slave. The SPI interface controller is a master responsible for the data transmission with the slave.

## 2.4.3.2 Pin Description

Table 2-3 SPI controller interface

| Signal name | Туре | Description                                   |  |  |  |

|-------------|------|-----------------------------------------------|--|--|--|

| CS_N        | 0    | Low active chip selection signal              |  |  |  |

| SCK         | 0    | The (bit) serial clock                        |  |  |  |

| MOSI        | 0    | Data signal from master output to slave input |  |  |  |

| MISO        | 1    | Data signal from slave output to master input |  |  |  |

#### 2.4.3.3 Transmission Formats

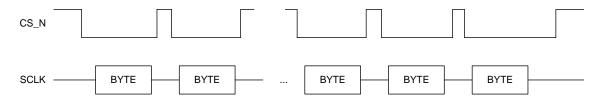

Figure 2-9 SPI transmission formats

The above figure shows the waveform during the SPI transmission. The low active CS\_N determines the start point and end point of one transaction. The CS\_N setup time, hold time and idle time are also depicted.

CPOL defines the clock polarity in the transmission. Two types of polarity can be adopted, i.e. polarity 0 and polarity 1. The above figure is an example of both clock polarities (CPOL).

CPHA defines the legal timing to sample MOSI and MISO. Two different methods can be adopted.

#### **2.4.3.4** Features

The features of the SPI controller (master) are:

- Configurable CS\_N setup time, hold time and idle time

- Programmable SCK high time and low time

- Configurable transmitting and receiving bit order

- Two configurable modes for the source of the data to be transmitted. 1) In Tx DMA mode, the SPI controller automatically fetches the transmitted data (to be put on the MOSI line) from memory. 2) In Tx FIFO mode, the data to be transmitted on the MOSI line are written to FIFO before the start of the transaction.

- Two configurable modes for destination of the data to be received. 1) In Rx DMA mode, the SPI controller automatically stores the received data (from MISO line) to memory. 2) In Rx FIFO mode, the received data keep being in Rx FIFO of the SPI controller. The processor must read back the data by itself.

- Adjustable endian order from/to memory system

- Programmable byte length for transmission

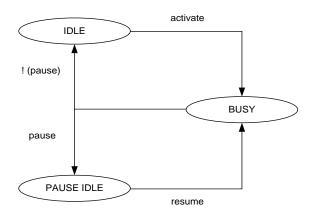

- Unlimited length for transmission. This is achieved by the operation of PAUSE mode. In PAUSE mode, the CS\_N signal will keep being active (low) after the transmission. At this time, the SPI controller is in PAUSE\_IDLE state, ready to receive the resume command. The state transition is shown in 錯誤! 找不到參照來源。10

- Configurable option to control CS\_N deassert between byte transfers. The controller supports a special

transmission format called CS\_N deassert mode. Figure 2-122 illustrates the waveform in this transmission

format.

Figure 2-10 Operation flow with or without PAUSE mode

Figure 2-11 CS\_N deassert mode

#### 2.4.4 SDIO Slave

## 2.4.4.1 Functional Description

The SD Input/Output (SDIO) card is based on and compatible with the SD memory card. The controller fully supports the SD memory card bus protocol as defined in SD Memory Card Specification Part 1 Physical Layer Specification version 2.0 and SDIO Specification version 2.0.

SDIO provides high-speed data IO with low power consumption. SDIO module provides an SDIO2.0 card interface connected to the host and can support multiple speed modes including default speed mode and high speed mode.

#### 2.4.4.2 Features

- SDIO 2.0 basic features

- 1-bit and 4-bit SD data transfer modes

- Default mode: Variable clock rate 0-25MHz, up to 12.5MB/sec interface speed (using 4 parallel data lines)

- High-Speed mode: Variable clock rate 0-50 MHz, up to 25MB/sec interface speed (using 4 data lines)

- CR and data port access

- Supports control register (CR) port single read/write access (AHB slave)

- Supports data port single and burst read/write access (AHB master)

- DMA function

- One TX channel and two Rx channels

- Moves TX data from HIF buffer to SYSRAM, TCM

- Moves RX data or firmware prepared data from SYSRAM, TCM to HIF buffer

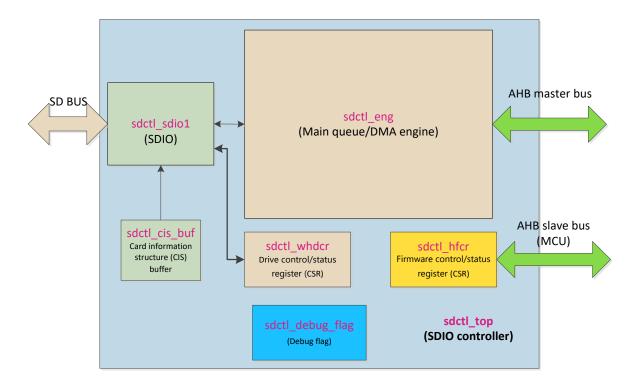

## 2.4.4.3 Block Diagram

The block diagram of the SDIO controller is shown in Figure 2-12

Figure 2-12 SDIO controller block diagram

# 2.4.4.4 Functions Description

From the external view, the SDIO interface mainly includes the SD bus and AHB master and slave. The AHB master is used for DMA operations and the AHB slave is used for register access from the MCU. The SD bus provides an interface for SD specification.

# 2.4.4.5 Pin description

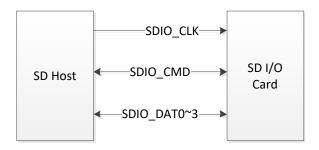

Figure 2-13 Signal connections to 4-bit SDIO cards

# Table 2-4 SDIO pin definitions

| Pin | Name      | SD 4-bit mode |                         | SD 1-bit mode |                   |

|-----|-----------|---------------|-------------------------|---------------|-------------------|

| 1   | SDIO_DAT3 | DAT[3]        | Data line3              | N/C           | Not used          |

| 2   | SDIO_CMD  | CMD           | Command line            | CMD           | Command<br>line   |

| 3   | VSS1      | VSS1          | Ground                  | VSS1          | Ground            |

| 4   | VDD       | VDD           | Supply voltage          | VDD           | Supply<br>voltage |

| 5   | SDIO_CLK  | CLK           | Clock                   | CLK           | Clock             |

| 6   | VSS2      | VSS2          | Ground                  | VSS2          | Ground            |

| 7   | SDIO_DAT0 | DAT[0]        | Data line0              | DATA          | Data line         |

| 8   | SDIO_DAT1 | DAT[1]        | Data line1 or interrupt | IRQ           | Interrupt         |

| 9   | SDIO_DAT2 | DAT[2]        | Data line2              | RW            | Not used          |

# 2.4.4.6 SDIO Timing Waveform (3.3V)

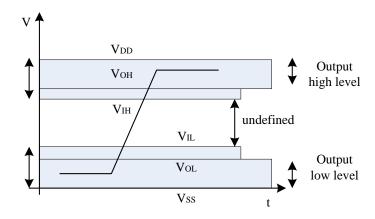

Figure 2-14 Bus signal levels

Table 2-5 Bus signal voltage

| Parameter           | Symbol | Min.      | Max.      | Unit | Conditions        |

|---------------------|--------|-----------|-----------|------|-------------------|

| Output High Voltage | VOH    | 0.75*VDD  |           | V    | IOH=-2mA VDD min  |

| Output Low Voltage  | VOL    |           | 0.125*VDD | V    | IOL = 2mA VDD min |

| Input High Voltage  | VIH    | 0.625*VDD | VDD+0.3   | V    |                   |

| Input Low Voltage   | VIL    | Vss-0.3   | 0.25*VDD  | V    |                   |

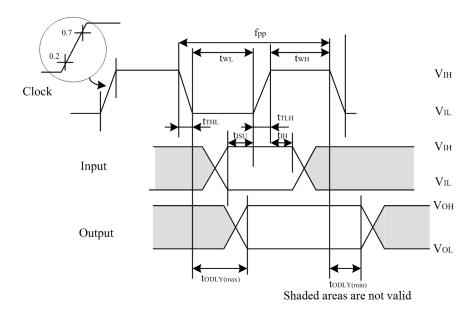

Figure 2-15 Bus timing diagram (default)

Table 2-6 Bus timing parameter values (default)

| Parameter                                                     | Symbol | Minimum | Maximum | Unit | Remark                 |  |  |  |

|---------------------------------------------------------------|--------|---------|---------|------|------------------------|--|--|--|

| Clock CLK (All values are referred to min (VIH) and max (VIL) |        |         |         |      |                        |  |  |  |

| Clock frequency data transfer mode                            | fPP    | 0       | 25      | MHz  | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock frequency identification mode                           | fOD    | 0/100   | 400     | kHz  | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock low time                                                | tWL    | 10      |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock high time                                               | tWH    | 10      |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock rise time                                               | tTLH   |         | 10      | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock fall time                                               | tTHL   |         | 10      | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Inputs CMD, DAT (referred to CLK)                             |        |         |         |      |                        |  |  |  |

| Input set-up time                                             | tISU   | 5       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Input hold time                                               | tIH    | 5       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Outputs CMD, DAT (referred to CLK)                            |        |         |         |      |                        |  |  |  |

| Output delay time during data transfer mode                   | tOLDY  | 0       | 14      | ns   | CL ≤ 40 pF (1 card)    |  |  |  |

| Output delay time during identification mode                  | tOLDY  | 0       | 50      | ns   | CL ≤ 40 pF (1 card)    |  |  |  |

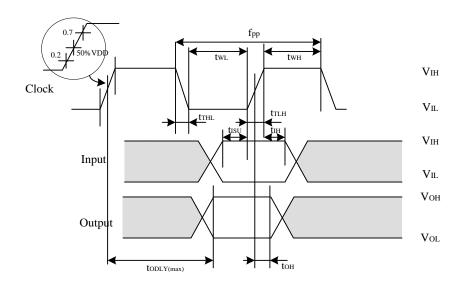

Figure 2-16 High-speed timing diagram

Table 2-7 High-speed timing parameter values

| Parameter                                                     | Symbol | Minimum | Maximum | Unit | Remark                 |  |  |  |

|---------------------------------------------------------------|--------|---------|---------|------|------------------------|--|--|--|

| Clock CLK (All values are referred to min (VIH) and max (VIL) |        |         |         |      |                        |  |  |  |

| Clock frequency data transfer mode                            | fPP    | 0       | 50      | MHz  | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock low time                                                | tWL    | 7       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock high time                                               | tWH    | 7       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock rise time                                               | tTLH   |         | 3       | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Clock fall time                                               | tTHL   |         | 3       | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Inputs CMD, DAT (referred to CLK)                             |        |         |         |      |                        |  |  |  |

| Input set-up time                                             | tISU   | 6       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Input hold time                                               | tIH    | 2       |         | ns   | CCARD ≤ 10 pF (1 card) |  |  |  |

| Outputs CMD, DAT (referred to CLK)                            |        |         |         |      |                        |  |  |  |

| Output delay time during data transfer mode                   | tOLDY  |         | 14      | ns   | CL ≤ 40 pF (1 card)    |  |  |  |

| Output hold time                                              | tOH    | 2.5     |         | ns   | CL ≥ 40 pF (1 card)    |  |  |  |

| Total system capacitance for each line (1)                    | CL     |         | 40      | pF   | 1 card                 |  |  |  |

<sup>(1)</sup> In order to satisfy the serving time, the host shall drive only one card.

# 2.4.5 I2C

#### 2.4.5.1 Introduction

There are two I2C master channels in the MT7931AN with the same HW architecture. I2C is a two-wire serial interface with two signals, SCL and SDA. SCL is a clock signal driven by the master. SDA is a bi-directional data signal that can be driven either by the master or by the slave. This generic controller supports the master role and conforms to the I2C specification.

#### **2.4.5.2** Features

The main supported features of I2C Master are as follows:

- I2C compliant master mode operation

- Adjustable clock speed for Fast-mode Plus

- 7-bit address

- Clock stretching feature

- START/STOP/repeated START conditions

- I2C\_FIFO mode

- DMA transfer mode

- Multi-write per transfer

- Multi-read per transfer

- Multi-transfer per transaction

- Combined format transfer with length change capability

- Multi-transfer with repeated START condition

# 2.4.5.3 Block Diagram

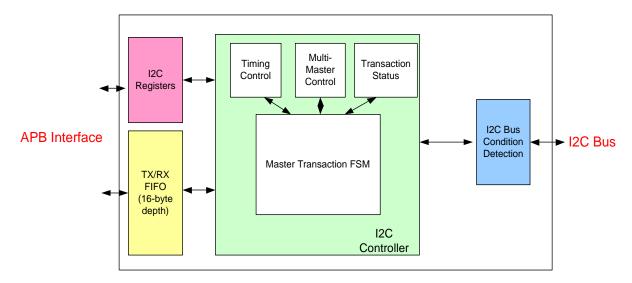

Figure 2-17 Block diagram of I2C

- I2C Registers: I2C configuration and status registers.

- Tx/Rx FIFO: Store the data to be sent to I2C slave or the data received from I2C slave.

- Master Transaction FSM: I2C master finite-state machine used to indicate the current transfer stage.

- Timing Control: Control the frequencies of SCL according to the configuration of CLOCK\_DIV, SAMPLE\_CNT\_DIV and STEP\_CNT\_DIV.

- Multi-Master Control: Execute arbitration when multiple masters exist on the I2C bus.

- Transaction Status: Record the number of bytes that has been transferred and the number of transfers that has been done. It can be used to judge if all transactions have been completed.

- I2C Bus Condition Detection: Detect START/STOP/repeated START conditions and clock stretching on the I2C bus.

#### 2.4.6 UART

#### 2.4.6.1 Introduction

The UART controller provides full duplex serial communication channels between the MT7931AN chip and external devices. The UART controller has M16C450 and M16550A operation modes, which are compatible with a range of standard software drivers. The extensions are designed to be broadly software compatible with 16550A variants, but certain areas offer no consensus.

In common with the M16550A, the UART controller supports word lengths from 5 to 8 bits, an optional parity bit and one or two stop bits, and this word length is fully programmable by a CPU interface. A 16-bit programmable baud rate generator and an 8-bit scratch register are included, along with separate transmission and received FIFOs. Eight modem control lines and a diagnostic loop-back mode are provided. The UART\_TOP also includes two DMA handshake lines which are used to indicate when the FIFOs are ready to transfer data to the CPU. Interrupts can be generated from any of the several sources.

After hardware reset, the UART controller is in M16C450 mode. Its FIFOs can be enabled and the UART controller can enter M16550A mode. The UART controller adds further functionality beyond M16550A mode. Each of the extended functions can be selected individually under software control.

#### **2.4.6.2** Features

- Provide 4 channels of UART controller

- UART TOP0, UART TOP1 and CM33 UART are 4-pin (TX, RX, CTS, RTS) UART TOP channel

- Support both M16C450 and M16550A operation modes

- Compatible with standard software drivers

- Transfer system: Asynchronous

- Data length: 5 to 8 bits

- Hardware flow control: CTS/RTS-based automatic transmission and reception of control

- Software flow control: Use special character XON/XOFF to do software flow control

- Baud rate is programmable from 300 bps to 3 Mbps

- Baud rate error: Less than 0.25 %

- Interrupt request: Receive interrupts/transmit interrupts

- Data transfer: DMA (Transmit/Receive) transfer is supported

#### 2.4.7 PWM

# 2.4.7.1 Functions Description

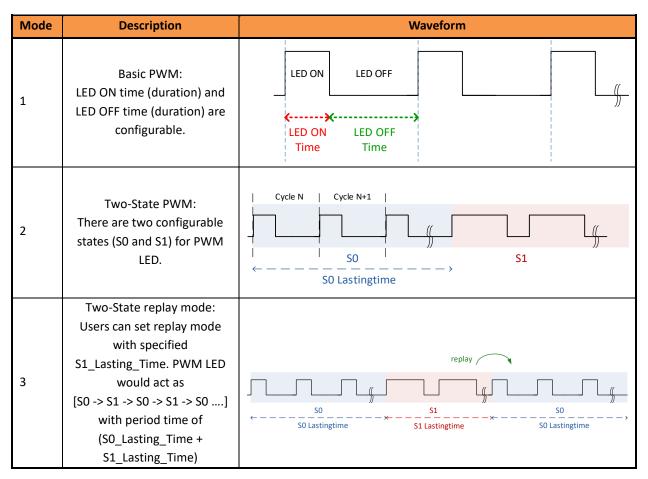

The MT7931AN features 2 generic PWMs to generate pulse sequences with programmable frequency and duration for LCD, vibrators, and other devices.

The PMU features three configurable pattern options.

Figure 2-18 PWM patterns

#### 2.4.8 DMA

Direct memory access (DMA) is used to transfer data between memory and memory as well as memory and peripherals without MCU interventions.

#### 2.4.8.1 Command Queue (CQ) DMA

The purpose of CQ\_DMA is to perform data transfer between memory and memory without CPU interventions.

The supported features of CQDMA are as below:

- Up to three channels of simultaneous data transfer are supported.

- Comply with the system bus (AXI).

- Two out-standings for three channels

- Source or destination address fix mode

- Source or destination address-wrapping mode

- Source and destination address-increment mode

- Fix-pattern mode

- Bandwidth limiter

- TrustZone

- Round-Robin (RR) for scheduling scheme

# 2.4.8.2 Application Processor (AP) DMA

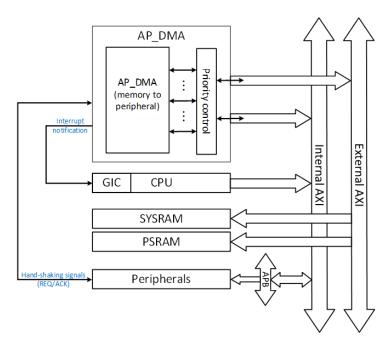

The purpose of APDMA is to perform data transfer between memory and peripherals.

The supported features of APDMA are as below:

- Up to 9 channels of simultaneous data transfer are supported.

- Comply with the system Bus (AXI)

- TrustZone

- Interrupt notification

- Round-Robin (RR) for scheduling scheme

There are 2 types of DMA channels supported in MT7931AN.

- Peripheral DMA: The behavior of Peripheral DMA is like that of CQ-DMA. The major difference is that the source or destination is peripherals FIFO, not memory.

- Virtual FIFO DMA (VFF DMA): It's a peripheral DMA with an additional FIFO control engine. It is used to provide the buffering capacity for peripherals.

### 2.4.8.2.1 Peripheral DMA

The behavior of Peripheral DMA is like that of CQ-DMA. The major difference is that the source or destination is peripheral FIFO, not memory. And there are handshaking signals (REQ / ACK) between DMA and peripheral. Because of handshaking signals, the DMA channels with corresponding peripheral channels are fixed.

Figure 2-19 APDMA Block Diagram

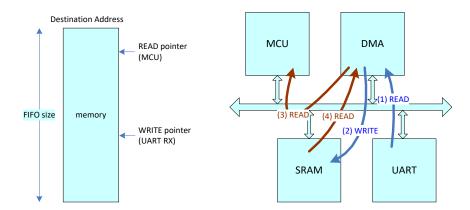

#### 2.4.8.2.2 Virtual FIFO

Virtual FIFO DMA is designed to offload the control of the serial interface. The difference between the virtual FIFO DMA and the peripheral DMA is that the virtual FIFO DMA contains an additional FIFO controller. VFF is like the ring buffer, and uses two address pointers (VFF\_WPT/VFF\_RPT) to control VFF condition. According to these two address pointers, two symbols are defined (VFF\_VALID\_SIZE/VFF\_LEFT\_SIZE) to represent the valid data and available space in VFF.

The figure below illustrates the operations of virtual FIFO DMA used for UART RX.

- (1) READ: DMA controller reads data from UART and increments the WRITE pointer of the FIFO controller.

- (2) WRITE; DMA controller writes data that was area from UART to SRAM in the area defined before enabling the virtual FIFO.

- (3) READ: MCU reads data when FIFO is not empty and the amount of data is over a pre-defined threshold. The read transaction will be finished only when DMA controller reads back the data from SRAM.

- (4) READ: DMA controller reads data from SRAM and increments the READ pointer of the FIFO controller.

Figure 2-20 Virtual FIFO Concept

### 2.4.8.2.3 APDMA Channels and Priority Control

There are totally 7 virtual FIFO DMA channels and 2 peripherals DMA channels in MT7931AN.

Table 2-8 DMA type for hardware IP

| Hardware IP       | DMA Type             |

|-------------------|----------------------|

| Radio (Bluetooth) | Virtual FIFO DMA x 2 |

| UART (x2)         | Virtual FIFO DMA x 4 |

| AUXADC            | Virtual FIFO DMA x 1 |

| I2C               | Peripheral DMA x 2   |

Page 38 of 77

#### 2.4.9 GPT

### 2.4.9.1 Introduction

The Application Processor X General Purpose Timer (APXGPT) module includes five 32-bit GPTs and one 64-bit GPT. Each GPT supports four operation modes, which are ONE-SHOT, REPEAT, KEEP-GO and FREERUN. Each GPT can be operated on one of the two clock sources, RTC clock (32.768 kHz) or system clock (13 MHz).

#### **2.4.9.2** Features

Table 2-9 provides the detailed information about the four operation modes for the GPT, ONE-SHOT, REPEAT, KEEP-GO and FREERUN.

Table 2-9 Operation Mode of GPT

| Mode         | Auto<br>Stop | Interrupt<br>Supported | Counting Behavior                                               | equals              | Example: Compare value is set to 2 (The bold value means interrupt asserted) |

|--------------|--------------|------------------------|-----------------------------------------------------------------|---------------------|------------------------------------------------------------------------------|

| ONE-<br>SHOT | Yes          | Yes                    | The GPT stops counting when GPTn_COUNT equals GPTn_COMPARE      | EN is reset to 0    | 0,1, <b>2</b> ,2,2,2,2,2,2,2,2,                                              |

| REPEAT       | No           | Yes                    | The GPT count is reset to 0 when GPTn_COUNT equals GPTn_COMPARE | Count is reset to 0 | 0,1 <b>,2</b> ,0,1, <b>2</b> ,0,1, <b>2</b> ,0,1, <b>2</b>                   |

| KEEP-GO      | No           | Yes                    | The GPT count is reset to 0 when overflow occurs                |                     | 0,1, <b>2</b> ,3,4,5,6,7,8,9,10,                                             |

| FREERUN      | No           | No                     | The GPT count is reset to 0 when overflow occurs                |                     | 0,1,2,3,4,5,6,7,8,9,10,                                                      |

#### Note:

Each timer's operation is independent and can be programmed to select the clock source, RTC clock (32.768 kHz) or system clock (13 MHz). After the clock source is determined, the division ratio of the selected clock can be programmed. The division ratio can be fine-granulated as 1 to 13 and coarse-granulated as 16, 32 and 64.

#### 2.4.9.3 Block Diagram

APXGPT consists of five sets of 32-bit GPTs and one set of 64-bit GPTs.

When the GPT triggers an IRQ, it will also issue a wakeup signal to "Sleep Control", and then "Sleep Control" can wake the MCU if the MCU is in sleep mode.

Figure 2-21 Block Diagram of APXGPT

### 2.4.9.4 Theory of Operations

For the GPT5 64-bit timer, the read operation of the 64-bit timer value will be separated into 2 APB reads since an APB read is of 32-bit width. To perform the read operation of 64-bit timer value, the lower word should be read first and then the higher word. The read operation of the lower word will freeze the "read value" of the higher word but will not freeze the timer counting. This ensures that the separated read operation acquires the correct timer value.

To program and use the GPT, please note:

The counter value can be read at any time when the clock source is system clock.

The counter value can be read at any time even when the clock source is RTC clock.

The comparative value can be programmed at any time. When the comparative value is rewritten during count operation, the counter will be reset to 0 and restart counting.

#### 2.4.10 WDT

#### 2.4.10.1 Introduction

The MT7931AN features a watchdog timer (WDT) for the Arm Cortex-M33 processor (referred to as CM33 in this document). CM33\_WDT is the watchdog timer for the Cortex-M33 processor. When the Cortex-M33 processor hangs due to some malfunctions, the watchdog timer is used to generate system alarm and trigger whole chip reset.

#### 2.4.10.2 Functional Description

The WDT provides the counter with the clock source of 32 kHz and asserts interrupt when needed. There is an interrupt counter, and it can operate as follows:

- One-shot mode: the timer stops when the timer counts down to zero.

- The timer counts from a programmable initial value and asserts interrupt when counting to zero. The interrupt will be level active low. The unit of the counter can be 1 x 32 kHz cycle.

The WDT provides two ways to generate the WDT event.

- Triggered by the time-out event to configure WDT HW reset mode.

- The WDT has an 11-bit counter and uses the 32-kHz clock. The software regularly restarts the timer to prevent it from expiring. If the timer fails to restart the WDT, it will expire and generate a WDT event.

- The programmable period length is 32ms\*(1~2048) which is ranged from 32ms to 65.5s.

- Triggered by software programming to write SW reset KEY.

#### 2.4.10.3 Event Notification for CM33

The WDT provides the following options when a WDT event is generated.

- Trigger whole chip reset

- Interrupt itself

Note: The reset whole chip option is included in top chip reset register space.

The WDT module can only be reset by the external reset (SYS\_RST\_N) and the PMU reset. Some WDT control registers feature a key protection mechanism to prevent unintentional access.

#### 2.4.11 GPIO

#### 2.4.11.1 Overview

The MT7931AN platform offers 23 General-Purpose Input/Output (GPIO) pins. By setting the control registers, the MCU software can control the direction and the output value of the GPIO pins and read the input value of these pins. The GPIO pins and GPO (General-Purpose Output) pins are multiplexed with other functions to reduce the pin count.

The clock to send data outside the chip is software configurable. There are six clock-out ports and each clock-out port can be programmed to output the appropriate clock source. In addition, when two GPIO pins function for the same peripheral IP, the smaller GPIO serial number has higher priority over the bigger one.

Figure 2-22 shows the block diagram of the GPIO controller in the MT7931AN.

Figure 2-22 MT7931AN GPIO Controller

# 2.4.11.2 I/O Pull up or Down Control Truth Table

All MT7931AN GPIO pins support both 1.8V and 3.3V IO power and different Pull up/Pull down resistors can be selected as Table 2-10.

Table 2-10 PU/PD resistance Spec

| E | PUPD | R1 | RO | R Value of 1.8V/3.3V IO<br>Power |

|---|------|----|----|----------------------------------|

| 0 | 0    | 0  | 0  | High-Z                           |

| 0 | 0    | 0  | 1  | PU10Kohm                         |

| 0 | 0    | 1  | 0  | PU50Kohm                         |

| 0 | 0    | 1  | 1  | PU10Kohm//50Kohm                 |

| 0 | 1    | 0  | 0  | High-Z                           |

| 0 | 1    | 0  | 1  | PD10Kohm                         |

| 0 | 1    | 1  | 0  | PD50Kohm                         |

| 0 | 1    | 1  | 1  | PD10Kohm//50Kohm                 |

| 1 | Х    | Х  | Х  | High-Z                           |

# 2.5 Interrupt

#### 2.5.1 Introduction

The MT7931AN embeds an interrupt controller, which is composed of an NVIC (Nested Vectored Interrupt Controller), a WIC (Wakeup Interrupt Controller) and a de-bounce circuit. The WIC and de-bounce circuit are in the Always-On domain. All internal or external interrupts are connected to the WIC as well as to the NVIC; thus, each interrupt signal can serve as wakeup source for the CM33 processor. And these interrupt sources could be level or edge triggered type by configuration.

## 2.5.2 Block Diagram

Figure 2-23 CM33\_IRQ Block Diagram

# 2.5.3 Interrupt Table

Table 2-11 CM33 interrupt

| MCU |                                          | e 2-11 CW33 Interrupt             |          |                       |     |

|-----|------------------------------------------|-----------------------------------|----------|-----------------------|-----|

| IRQ | Interrupt Name                           | Interrupt Description             | Polarity | Edge /                | EIN |

| NUM | interrupe Nume                           | interrupt Description             | Tolarity | Level                 | Т   |

| 0   | wic_int_wake_up                          | WIC wakeup interrupt to CM33      | н        | edge(HW)<br>level(SW) | х   |

| 1   | Reserved                                 |                                   |          |                       |     |

| 2   | Reserved                                 |                                   |          |                       |     |

| 3   | ~wdt_irq_b0                              | CM33 WDT interrupt (wdt_irq_b[0]) | Н        | edge                  | Х   |

| 4   | ~uart_irq_b                              | CM33 UART interrupt               | Н        | level                 | Х   |

| 5   | infra_bus_int                            | Infra bus error interrupt         | Н        | level                 | Х   |

| 6   | dbgsys_CDBGPWRUPREQ                      | CoreSight debug power up req      | Н        | level                 | Х   |

| 7   | dbgsys_CDBGPWRUPACK                      | CoreSight debug power up ack      | Н        | level                 | Х   |

| 8   | andt ira b1                              | CM33 WDT interrupt                | Н        | level                 | Х   |

| ٥   | ~wdt_irq_b1                              | (wdt_irq_b[1])                    | "        |                       | ^   |

| 9   | Reserved                                 |                                   |          |                       |     |

| 10  | ~apxgpt_irq_b0[0]                        | GPT_32_0                          | Н        | level                 | Х   |

| 11  | ~apxgpt_irq_b0[1]                        | GPT_32_1                          | Н        | level                 | Х   |

| 12  | ~apxgpt_irq_b0[2]                        | GPT_32_2                          | Н        | level                 | Х   |

| 13  | ~apxgpt_irq_b0[3]                        | GPT_32_3                          | Н        | level                 | Х   |

| 14  | ~apxgpt_irq_b0[4]                        | GPT_32_4                          | Н        | level                 | Х   |

| 15  | ~apxgpt_irq_b0[5]                        | GPT_64                            | Н        | level                 | Х   |

| 16  | ~devapc_INFRA_AON_secure_vio_ir<br>q_b   | devapc secure violate             | Н        | level                 | х   |

| 17  | ~devapc_AUD_BUS_PDN_secure_vi<br>o_irq_b | AUDIO_BUS devapc secure violate   | Н        | level                 | х   |

| 18  | conn_ap_bus_req_rise_irq                 | conn_ap_bus_req rising edge IRQ   | Н        | level                 | х   |

| 19  | conn_ap_bus_req_fall_irq                 | conn_ap_bus_req falling edge IRQ  | Н        | level                 | х   |

| 20  | conn_apsrc_req_rise_irq                  | conn_apsrc_req rising edge IRQ    | Н        | level                 | Х   |

| 21  | conn_apsrc_req_fall_irq                  | conn_apsrc_req falling edge IRQ   | Н        | level                 | Х   |

| 22  | conn_ap_bus_req_high_irq                 | conn_ap_bus_req level high IRQ    | Н        | level                 | Х   |

| 23  | conn_ap_bus_req_low_irq                  | conn_ap_bus_req level low IRQ     | Н        | level                 | Х   |

| 24  | conn_apsrc_req_high_irq                  | conn_apsrc_req level high IRQ     | Н        | level                 | Х   |

| 25  | conn_apsrc_req_low_irq                   | conn_apsrc_req level low IRQ      | Н        | level                 | Х   |

| 26  | infra_bus_timeout_irq                    | infra bus timeout IRQ             | Н        | level                 | Х   |

| MCU |                          |                                                 |          |        |     |

|-----|--------------------------|-------------------------------------------------|----------|--------|-----|

| IRQ | Interrupt Name           | Interrupt Description                           | Polarity | Edge / | EIN |

| NUM |                          |                                                 | <b>_</b> | Level  | T   |

| 27  | cm33_local_bus_int       | CM33 local bus interrupt                        | Н        | level  | Х   |

| 28  | Reserved                 |                                                 |          |        |     |

| 29  | Reserved                 |                                                 |          |        |     |

| 30  | Reserved                 |                                                 |          |        |     |

| 31  | Reserved                 |                                                 |          |        |     |

| 32  | Reserved                 |                                                 |          |        |     |

| 33  | ~top_uart0_irq_b         | TOP UART                                        | Н        | level  | Х   |

| 34  | ~top_uart1_irq_b         | TOP UART                                        | Н        | level  | Х   |

| 35  | ~i2c0_irqb               | I2C transfer done or error                      | Н        | level  | Х   |

| 36  | ~i2c1_irqb               | I2C transfer done or error                      | Н        | level  | Х   |

| 37  | ~sdctl_top_fw_irq_b      | SDIO slave interrupt                            | Н        | level  | Х   |

| 38  | ~sdctl_top_fw_irq_b_qout | SDIO slave interrupt                            | Н        | level  | Х   |

| 39  | ~spi_irq_b               | SPI master transfer done or pause               | Н        | level  | Х   |

| 40  | ~spi_irq_b               | SPI master transfer done or pause               | н        | level  | х   |

| 41  | Reserved                 |                                                 |          |        |     |

| 42  | Reserved                 |                                                 |          |        |     |

| 43  | ~irrx_irq_b              | IRRX decoding done                              | Н        | level  | Х   |

| 44  | Reserved                 |                                                 |          |        |     |

| 45  | Reserved                 |                                                 |          |        |     |

| 46  | Reserved                 |                                                 |          |        |     |

| 47  | Reserved                 |                                                 |          |        |     |

| 48  | Reserved                 |                                                 |          |        |     |

| 49  | Reserved                 |                                                 |          |        |     |

| 50  | Reserved                 |                                                 |          |        |     |

| 51  | ~audio_irq_mcu_b         | AFE interrupt                                   | Н        | level  | Х   |

| 52  | Reserved                 |                                                 |          |        |     |

| 53  | sysram_top_int           | SYSRAM out-of-bound access error                | Н        | level  | х   |

| 54  | ~mpu_irq_b_l2_pwr        | illegal accesses to asic_mpu<br>instances in L2 | Н        | level  | х   |

| 55  | ~mpu_irq_b_psram_pwr     | illegal accesses to asic_mpu for PSRAM          | Н        | level  | х   |

| 56  | ~cq_dma_irq_b[0]         | CQ_DMA Channel 0 finishes operation             | Н        | level  | х   |

| MCU      |                                                 |                                               |          | - · · / |          |

|----------|-------------------------------------------------|-----------------------------------------------|----------|---------|----------|

| IRQ      | Interrupt Name Interrupt Description            |                                               | Polarity | Edge /  | EIN      |

| NUM      |                                                 |                                               |          | Level   | T        |

| F 7      | You done is b[1]                                | CQ_DMA Channel 1 finishes                     |          | level   | V        |

| 57       | ~cq_dma_irq_b[1]                                | operation                                     | Н        | levei   | X        |

| 58       | ~cq_dma_irq_b[2]                                | CQ_DMA Channel 2 finishes                     | Н        | level   | Х        |

| 36       | cq_uma_mq_b[2]                                  | operation                                     | '        | level   | ^        |

| 59       | ~msdc_irq_b_0p                                  | normal IRQ                                    | Н        | level   | Χ        |

| 60       | ~msdc_wakeup_ps_0p                              | wakeup IRQ                                    | Н        | level   | Χ        |

| 61       | Reserved                                        |                                               |          |         |          |

| 62       | Reserved                                        |                                               |          |         |          |

| 63       | ~ap_dma_irq_b[0]                                | AP_DMA Channel 0 (I2C 0)                      | Н        | level   | Х        |

| 03       | ap_uma_mq_b[o]                                  | finishes operation                            | 11       | ievei   | <b>X</b> |

| 64       | ~ap_dma_irq_b[1]                                | AP_DMA Channel 1 (I2C 1)                      | Н        | level   | Х        |

| 04       | ap_ama_nq_o[±]                                  | finishes operation                            |          | icvei   | ^        |

| 65       | ~ap_dma_irq_b[2]                                | AP_DMA Channel 2 (Reserved)                   | н        | level   | X        |

|          | ap_ama_nq_s[2]                                  | finishes operation                            | ''       |         |          |

| 66       | ~ap_dma_irq_b[3]                                | AP_DMA Channel 3 (Reserved)                   | Н        | level   | X        |

|          | ap_aa_a[o]                                      | finishes operation                            |          |         |          |

| 67       | ~ap_dma_irq_b[4]                                | AP_DMA Channel 4 (UART 0 TX)                  | Н        | level   | Х        |

|          |                                                 | finishes operation                            |          |         |          |

| 68       | ~ap_dma_irq_b[5]                                | AP_DMA Channel 5 (UART 0 RX)                  | н        | level   | Х        |

|          |                                                 | finishes operation                            |          |         |          |